SLVS798F-JANUARY 2008-REVISED NOVEMBER 2008

**TPS2062A**

**TPS2066A**

## TWO CHANNEL, CURRENT-LIMITED, POWER-DISTRIBUTION SWITCHES

#### FEATURES

- 70-mΩ High-Side MOSFET

- **1-A Continuous Current**

- Thermal and Short-Circuit Protection

- Accurate Current-Limit (1.2 A min, 2 A max)

- Operating Range: 2.7 V to 5.5 V

- 0.6-ms Typical Rise Time .

- **Undervoltage Lockout**

- Deglitched Fault Report (OCx)

- No OCx Glitch During Power Up

- 1-µA Maximum Standby Supply Current

- **Bidirectional Switch**

- Ambient Temperature Range: -40°C to 85°C

- **Built-in Soft-Start**

- UL Listed -- File No. E169910, Both Single and **Ganged Channel Configuration**

### APPLICATIONS

- **Heavy Capacitive Loads** •

- **Short-Circuit Protection**

Enable inputs are active low for all TPS2062A and active high for all TPS2066A

#### DESCRIPTION

The TPS206xA power-distribution switches are intended for applications where heavy capacitive loads and short-circuits are likely to be encountered. The TPS206xA family is pin-for-pin compatible with the TPS206x family with a tighter overcurrent tolerance. This family of devices incorporates two 70-mΩ N-channel MOSFET power switches for power-distribution systems that require multiple power switches in a single package. Each switch is controlled by a logic enable input. Gate drive is provided by an internal charge pump designed to control the power-switch rise and fall times to minimize current surges during switching. The charge pump requires no external components and allows operation from supplies as low as 2.7 V.

Each device limits the output current to a safe level by switching into a constant-current mode when the output load exceeds the current-limit threshold or a short is present. Individual channels indicate the presence of an overcurrent condition by asserting its corresponding OCx output (active low). Thermal protection circuitry disables the device during overcurrent or short-circuit events to prevent permanent damage. The device recovers from thermal shutdown automatically once the device has cooled sufficiently. The device provides undervoltage lockout to disable the device until the input voltage rises above 2.0 V. The TPS206xA is designed to current limit at 1.6 A typically per channel.

|                                                                                               | GENERAL SWITCH CATALOG                                                                                                                                                                                  |                                                                                                                                                              |                                                                                                                                |                                                                                                                                     |                    |             |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--|--|--|--|--|

| <b>33 mΩ, single</b><br><u>1000</u><br>TPS201xA 0.2A-2A<br>TPS202x 0.2A-2A<br>TPS203x 0.2A-2A | 80 mΩ, single<br>TPS2014 600 mA<br>TPS2015 1A<br>TPS20515 500 mA<br>TPS2041B 500 mA<br>TPS2045A 250 mA<br>TPS2045A 250 mA<br>TPS2055A 250 mA<br>TPS2065 1A<br>TPS2065 1A<br>TPS2065 1A<br>TPS2069 1.5 A | <b>80 mΩ, dual</b><br>TPS2042B 500 mA<br>TPS2042B 500 mA<br>TPS2046B 250 mA<br>TPS2046B 250 mA<br>TPS2062 1A<br>TPS2066 1A<br>TPS2066 1.5 A<br>TPS2064 1.5 A | <b>80 mΩ, dual</b><br>TPS2080 500 mA<br>TPS2081 500 mA<br>TPS2082 500 mA<br>TPS2090 250 mA<br>TPS2091 250 mA<br>TPS2092 250 mA | <b>80 mΩ, triple</b><br>TPS2043B 500 mA<br>TPS2053B 500 mA<br>TPS2047B 250 mA<br>TPS2047B 250 mA<br>TPS2067 A 250 mA<br>TPS2067 1 A | <b>80 mΩ, quad</b> | 80 mΩ, quad |  |  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

#### TPS2062A TPS2066A SLVS798F-JANUARY 2008-REVISED NOVEMBER 2008

www.ti.com

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C, Method 3015; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriate logic voltage level, preferably either VCC or ground. Specific guidelines for handling devices of this type are contained in the publication Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies available from Texas Instruments.

#### **AVAILABLE OPTION AND ORDERING INFORMATION**

|                |                | RECOMMENDED                |                                   |             | PAC       | KAGE <sup>(1)</sup> |           |  |

|----------------|----------------|----------------------------|-----------------------------------|-------------|-----------|---------------------|-----------|--|

| T <sub>A</sub> | ENABLE         | MAXIMUM<br>CONTINUOUS LOAD | TYPICAL<br>SHORT-CIRCUIT<br>LIMIT | D-i<br>(SOI | -         | DRB-8<br>(SON)      |           |  |

|                |                | CURRENT                    | 2                                 | PART #      | STATUS    | PART #              | STATUS    |  |

| –40°C to       | Active<br>low  | 1.0                        | 16.4                              | TPS2062AD   | AVAILABLE | TPS2062ADRB         | AVAILABLE |  |

| 85°C           | Active<br>high |                            | 1.6 A TPS2066AD                   |             | AVAILABLE | TPS2066ADRB         | AVAILABLE |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating temperature range unless otherwise noted<sup>(1)(2)</sup>

|                  |                                    |                               | VALUE                          | UNIT |

|------------------|------------------------------------|-------------------------------|--------------------------------|------|

| VI               | Input voltage range                | IN                            | -0.3 to 6                      | V    |

| Vo               | Output voltage range               | OUTx                          | -0.3 to 6                      | V    |

| V                | Input voltage range                | ENx, ENx                      | -0.3 to 6                      | V    |

| VI               | Voltage range                      | <u>OCx</u>                    | -0.3 to 6                      | V    |

| I <sub>O</sub>   | Continuous output current          | OUTx                          | Internally limited             |      |

|                  | Continuous total power dissipation | on                            | See "Dissipation Rating Table" |      |

| TJ               | Operating junction temperature     | range                         | -40 to 125                     | °C   |

| T <sub>stg</sub> | Storage temperature range          |                               | -65 to 150                     | °C   |

| ESD              | Electrostatic discharge            | Human body model MIL-STD-883C | 2                              | kV   |

| E3D              | protection                         | Charge device model (CDM)     | 500                            | V    |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND.

### **DISSIPATION RATING TABLE**

| BOARD                 | PACKAGE            | $\begin{array}{c} \textbf{THERMAL} \\ \textbf{RESISTANCE } \boldsymbol{\theta}_{\textbf{JA}} \end{array}$ | T <sub>A</sub> ≤ 25°C<br>POWER<br>RATING | DERATING<br>FACTOR<br>ABOVE $T_A = 25^{\circ}C$ | T <sub>A</sub> = 70°C<br>POWER<br>RATING | T <sub>A</sub> = 85°C<br>POWER<br>RATING |

|-----------------------|--------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------|------------------------------------------|------------------------------------------|

| Low-K <sup>(1)</sup>  | D-8                | 170 °C/W                                                                                                  | 586 mW                                   | 5.86 mW/°C                                      | 320 mW                                   | 234 mW                                   |

| High-K <sup>(2)</sup> | D-8                | 97.5 °C/W                                                                                                 | 1025 mW                                  | 10.26 mW/°C                                     | 564 mW                                   | 410 mW                                   |

| Low-K <sup>(3)</sup>  | DRB <sup>(4)</sup> | 270 °C/W                                                                                                  | 370 mW                                   | 3.71 mW/°C                                      | 203 mW                                   | 148 mW                                   |

| High-K <sup>(5)</sup> | DRB <sup>(4)</sup> | 60 °C/W                                                                                                   | 1600 mW                                  | 16.67 mW/°C                                     | 916 mW                                   | 666 mW                                   |

The JEDEC low-K (1s) board used to dervice this data was a 3in x 3in, two-layer board with 2-ounce copper traces on top of the board.

The JEDEC high-K (2s2p) board used to dervice this data was a 3in x 3in, multilayer board with 1-ounce internal power and ground

planes and 2-ounce copper traces on top and bottom of the board.

(3) Soldered PowerPAD on a standard 2-layer PCB without vias for thermal pad. See TI application note SLMA002 for further details.

(4) See Recommended Operating Conditions Table for PowePad connection guidelines to meet qualifying conditions for CB Certificate

(5) Soldered PowerPAD on a standard 4-layer PCB with vias for thermal pad. See TI application note SLMA002 for further details.

#### **RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>**

|                |                                        | MIN | MAX | UNIT |

|----------------|----------------------------------------|-----|-----|------|

| Vi             | Input voltage, IN                      | 2.7 | 5.5 | V    |

| ٧I             | Input voltage, ENx, ENx                | 0   | 5.5 | V    |

| I <sub>O</sub> | Continuous output current, OUTx        | 0   | 1   | А    |

| TJ             | Operating virtual junction temperature | -40 | 125 | °C   |

(1) The PowePad must be connected externally to GND pin to meet qualifying conditions for CB Certificate (DRB package only)

### **ELECTRICAL CHARACTERISTICS**

over recommended operating junction temperature range,  $V_I = 5.5 \text{ V}$ ,  $I_O = 1 \text{ A}$ ,  $V_{/ENx} = 0 \text{ V}$  (TPS2062A) or  $V_{ENx} = 5.5 \text{ V}$  (unless otherwise noted)

|                     | PARAMETER                               |                                                                                                                                                                                                                                                               | MIN                                                                 | TYP                                                                   | MAX  | UNIT |      |    |  |

|---------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|----|--|

| POWER S             | WITCH                                   |                                                                                                                                                                                                                                                               |                                                                     |                                                                       |      |      |      |    |  |

| _                   | Statia drain aguras en stata registance | 2.7 V $\leq$ V <sub>1</sub> $\leq$ 5.5 V, I <sub>0</sub> = 1 A                                                                                                                                                                                                |                                                                     |                                                                       | 70   | 100  | mΩ   |    |  |

| r <sub>DS(on)</sub> | Static drain-source on-state resistance | $2.7 \text{ V} \leq \text{V}_1 \leq 5.5 \text{ V}_2$                                                                                                                                                                                                          | $V, I_0 = I A$                                                      | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ |      |      | 135  | mu |  |

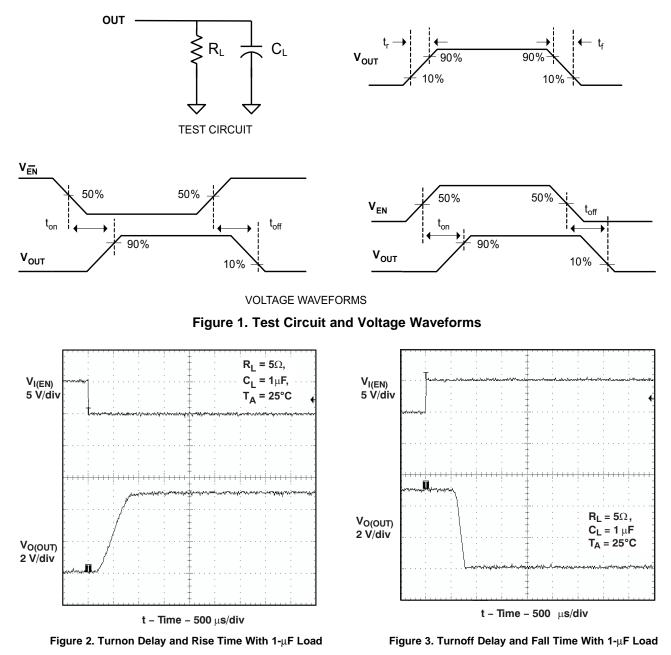

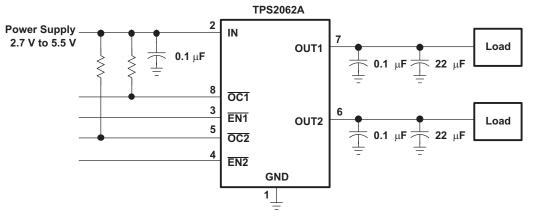

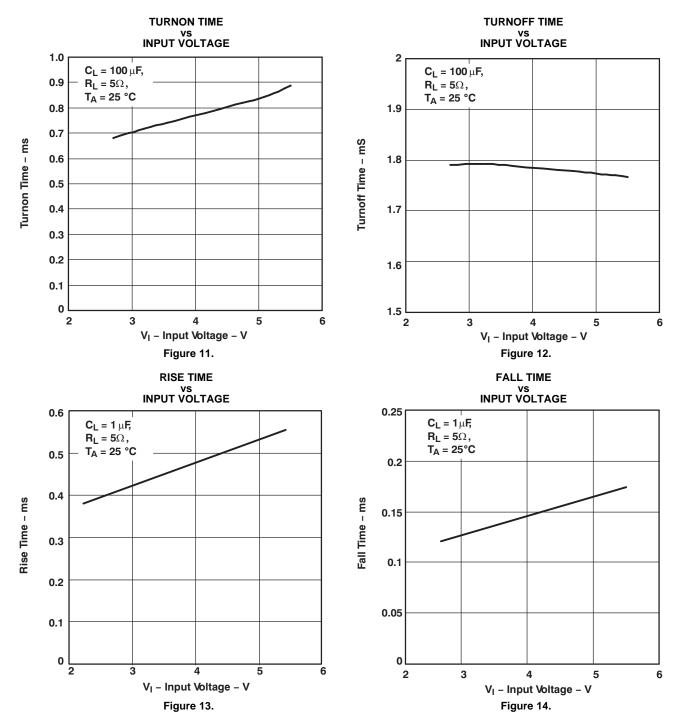

|                     | Diss time, sutput                       | V <sub>I</sub> = 5.5 V                                                                                                                                                                                                                                        |                                                                     |                                                                       |      | 0.6  | 1.5  |    |  |

| t <sub>r</sub>      | Rise time, output                       | V <sub>I</sub> = 2.7 V                                                                                                                                                                                                                                        | $C_{1} = 1  \mu F$ ,                                                |                                                                       |      | 0.4  | 1    |    |  |

|                     | Fall time, output                       | V <sub>I</sub> = 5.5 V                                                                                                                                                                                                                                        | $C_{L} = 1 \ \mu F,$<br>$R_{L} = 5 \ \Omega, \ T_{J} = 25^{\circ}C$ |                                                                       | 0.05 |      | 0.5  | ms |  |

| t <sub>f</sub>      |                                         | V <sub>I</sub> = 2.7 V                                                                                                                                                                                                                                        |                                                                     |                                                                       | 0.05 |      | 0.5  |    |  |

| ENABLE I            | NPUT EN OR EN                           |                                                                                                                                                                                                                                                               |                                                                     |                                                                       |      |      |      |    |  |

| V <sub>IH</sub>     | High-level input voltage                | 271/21/2551                                                                                                                                                                                                                                                   | 1                                                                   |                                                                       | 2    |      |      | V  |  |

| V <sub>IL</sub>     | Low-level input voltage                 | $2.7 V \le V_1 \le 5.5 V_2$                                                                                                                                                                                                                                   | <i>I</i>                                                            |                                                                       |      |      | 0.8  | V  |  |

| I <sub>I</sub>      | Input current                           |                                                                                                                                                                                                                                                               |                                                                     |                                                                       | -0.5 |      | 0.5  | μΑ |  |

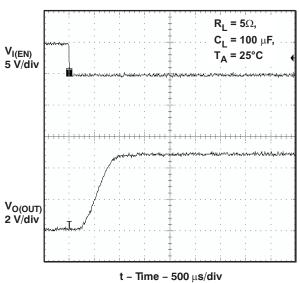

| t <sub>on</sub>     | Turnon time                             | C = 100E B                                                                                                                                                                                                                                                    | - 5 0                                                               |                                                                       |      |      | 3    |    |  |

| t <sub>off</sub>    | Turnoff time                            | $C_{L} = 100 \ \mu F, R_{L}$                                                                                                                                                                                                                                  | = 5 17                                                              |                                                                       |      |      | 3    | ms |  |

| CURRENT             | LIMIT                                   |                                                                                                                                                                                                                                                               |                                                                     |                                                                       |      |      |      |    |  |

|                     | Short-circuit output current per        | $V_1 = 5 V, OUTx c$                                                                                                                                                                                                                                           | connected to GND,                                                   | $T_J = 25^{\circ}C$                                                   | 1.2  | 1.6  | 2.0  | •  |  |

| l <sub>os</sub>     | channel                                 |                                                                                                                                                                                                                                                               |                                                                     | $-40^{\circ}$ C ≤ T <sub>J</sub> ≤ 125°C                              | 1.1  | 1.6  | 2.1  | A  |  |

| l <sub>oc</sub>     | Overcurrent trip threshold              | V <sub>IN</sub> = 5 V                                                                                                                                                                                                                                         |                                                                     |                                                                       |      | 2.1  | 2.45 | А  |  |

|                     |                                         | $ \begin{array}{l} V_{I} = 5 \ V, \ \text{OUT1 \& OUT2 connected to} \\ \text{GND, device enabled into short-circuit} \end{array} \begin{array}{l} T_{J} = 25^{\circ}\text{C} \\ \hline -40^{\circ}\text{C} \leq T_{J} \leq 125^{\circ}\text{C} \end{array} $ |                                                                     | $T_J = 25^{\circ}C$                                                   | 2.4  | 3.2  | 4.0  |    |  |

| I <sub>OS_G</sub>   | Ganged short-circuit output current     |                                                                                                                                                                                                                                                               |                                                                     | $-40^{\circ}$ C ≤ T <sub>J</sub> ≤ 125°C                              | 2.2  | 3.2  | 4.2  | А  |  |

| I <sub>OC_G</sub>   | Ganged overcurrent trip threshold       | V <sub>I</sub> = 5 V, OUT1 & OUT2 tied together                                                                                                                                                                                                               |                                                                     |                                                                       |      | 4.2  | 4.9  |    |  |

| SUPPLY C            | URRENT                                  | ·                                                                                                                                                                                                                                                             |                                                                     |                                                                       |      |      |      |    |  |

|                     |                                         | $T_J = 25^{\circ}C$                                                                                                                                                                                                                                           |                                                                     |                                                                       |      | 0.5  | 1    |    |  |

| IIL                 | Supply current, device disabled         | No load on OUT                                                                                                                                                                                                                                                |                                                                     | $-40^{\circ}$ C ≤ T <sub>J</sub> ≤ 125°C                              |      | 0.5  | 5    | μA |  |

|                     |                                         | No load on OUT                                                                                                                                                                                                                                                |                                                                     | $T_J = 25^{\circ}C$                                                   |      | 50   | 60   |    |  |

| l <sub>IH</sub>     | Supply current, device enabled          | No load on OUT                                                                                                                                                                                                                                                |                                                                     | $-40^{\circ}$ C ≤ T <sub>J</sub> ≤ 125°C                              |      | 50   | 75   | μA |  |

| l <sub>ikg</sub>    | Leakage current, device disabled        | OUT connected                                                                                                                                                                                                                                                 | to ground                                                           | $-40^{\circ}$ C ≤ T <sub>J</sub> ≤ 125°C                              |      | 1    |      | μΑ |  |

| Reverse lea         | akage current                           | $V_0 = 5.5 V, V_1 =$                                                                                                                                                                                                                                          | 0 V                                                                 | $T_J = 25^{\circ}C$                                                   |      | 0.2  |      | μΑ |  |

| UNDERVO             | LTAGE LOCKOUT                           | ·                                                                                                                                                                                                                                                             |                                                                     |                                                                       |      |      |      |    |  |

|                     | Low-level input voltage, IN             | V <sub>I</sub> rising                                                                                                                                                                                                                                         |                                                                     |                                                                       | 2    |      | 2.5  | V  |  |

|                     | Hysteresis, IN                          | V <sub>I</sub> falling                                                                                                                                                                                                                                        |                                                                     |                                                                       |      | 75   |      | mV |  |

| OVERCUR             | RENT FLAG                               |                                                                                                                                                                                                                                                               |                                                                     |                                                                       |      |      |      |    |  |

| V <sub>OL</sub>     | Output low voltage, OC                  | I <sub>/OCx</sub> = 5 mA                                                                                                                                                                                                                                      |                                                                     |                                                                       |      |      | 0.4  | V  |  |

|                     | Off-state current                       | V <sub>/OCx</sub> = 5.0 V or 3                                                                                                                                                                                                                                | 3.3 V                                                               |                                                                       |      |      | 1    | μΑ |  |

|                     | OC deglitch                             | OCx assertion or                                                                                                                                                                                                                                              | de-assertion                                                        |                                                                       | 4    | 8    | 15   | ms |  |

| THERMAL             | SHUTDOWN <sup>(2)</sup>                 |                                                                                                                                                                                                                                                               |                                                                     |                                                                       | 1    |      |      |    |  |

| Thermal sh          | nutdown threshold                       |                                                                                                                                                                                                                                                               |                                                                     |                                                                       | 135  |      |      | °C |  |

| Recovery fr         | rom thermal shutdown                    |                                                                                                                                                                                                                                                               |                                                                     |                                                                       | 125  |      |      | °C |  |

| Hysteresis          |                                         |                                                                                                                                                                                                                                                               |                                                                     |                                                                       |      | 10   |      | °C |  |

(1) Pulsed load testing used to maintain junction temperature close to ambient

(2) The thermal shutdown only reacts under overcurrent conditions.

### **DEVICE INFORMATION**

#### **Terminal Functions**

|                           | TERMINAL |          | I/O | DESCRIPTION                                                                 |  |  |  |  |

|---------------------------|----------|----------|-----|-----------------------------------------------------------------------------|--|--|--|--|

| NAME                      | TPS2062A | TPS2066A | 1/0 | DESCRIPTION                                                                 |  |  |  |  |

| EN1                       | 3        | —        | I   | Enable input, logic low turns on power switch IN-OUT1                       |  |  |  |  |

| EN2                       | 4        | —        | I   | Enable input, logic low turns on power switch IN-OUT2                       |  |  |  |  |

| EN1                       | _        | 3        | I   | Enable input, logic high turns on power switch IN-OUT1                      |  |  |  |  |

| EN2                       | _        | 4        | I   | Enable input, logic high turns on power switch IN-OUT2                      |  |  |  |  |

| GND                       | 1        | 1        |     | Ground                                                                      |  |  |  |  |

| IN                        | 2        | 2        | I   | Input voltage                                                               |  |  |  |  |

| OC1                       | 8        | 8        | 0   | Channel 1 over-current indicator; the output is open-drain, active low type |  |  |  |  |

| OC2                       | 5        | 5        | 0   | Channel 2 over-current indicator; the output is open-drain, active low type |  |  |  |  |

| OUT1                      | 7        | 7        | 0   | Power-switch output, IN-OUT1                                                |  |  |  |  |

| OUT2                      | 6        | 6        | 0   | Power-switch output, IN-OUT2                                                |  |  |  |  |

| PowerPAD <sup>™ (1)</sup> | PAD      | PAD      |     | Connect PowerPAD to GND for proper operation (DRB package only)             |  |  |  |  |

(1) See the Recommended Operating Conditions Table for PowePad connection guidelines to meet qualifying conditions for CB Certificate.

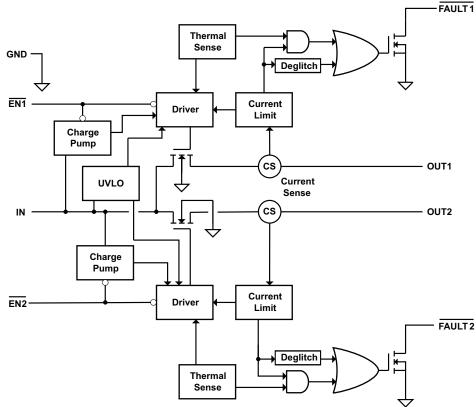

# FUNCTIONAL BLOCK DIAGRAM

A. Current sense

4

B. Active low (ENx) for TPS2062A. Active high (ENx) for TPS2066A.

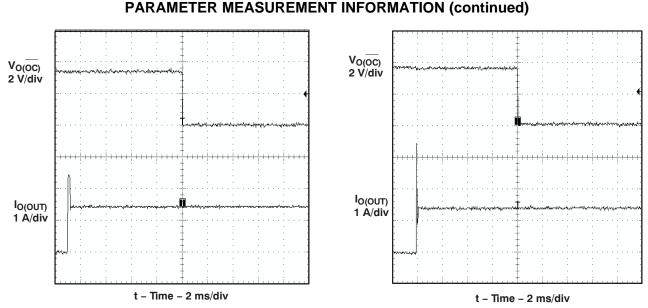

#### PARAMETER MEASUREMENT INFORMATION

Copyright © 2008, Texas Instruments Incorporated

$R_L = 5\Omega$ ,

$C_L = 100 \ \mu$ F, T<sub>A</sub> = 25°C

www.ti.com

V<sub>I(EN)</sub> 5 V/div

V<sub>O(OUT)</sub> 2 V/div

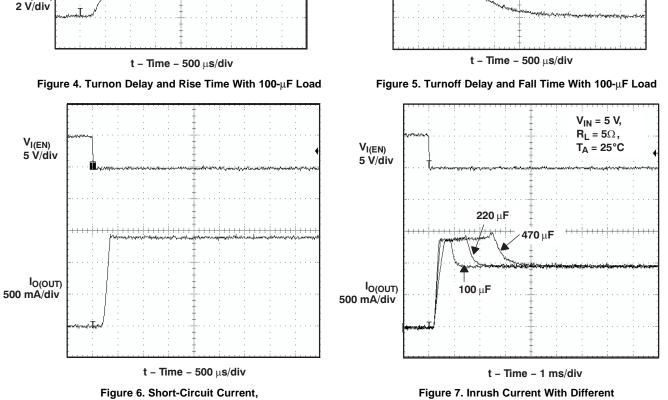

**Device Enabled Into Short**

Load Capacitance

Figure 9. 1-Ω Load Connected to Enabled Device

#### **POWER-SUPPLY CONSIDERATIONS**

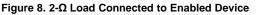

Figure 10. Typical Application

#### DETAILED DESCRIPTION

#### **OVERVIEW**

The devices are current-limited, power distribution switches using N-channel MOSFETs for applications where short-circuits or heavy capacitive loads will be encountered. These devices have a minimum fixed current-limit threshold above 1.1 A allowing for continuous operation up to 1 A per channel. Overtemperature protection is an additional device shutdown feature. Each device incorporates an internal charge pump and gate drive circuitry necessary to drive the N-channel MOSFETs. The charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V and requires little supply current. The driver controls the gate voltage of the power switch. The driver incorporates circuitry that controls the rise and fall times of the output voltage to provide "soft-start" and to limit large current and voltage surges.

Copyright © 2008, Texas Instruments Incorporated

TPS2062A TPS2066A SLVS798F-JANUARY 2008-REVISED NOVEMBER 2008

www.ti.com

#### OVERCURRENT

When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Three possible overload conditions can occur.

In the first condition, the output has been shorted before the device is enabled or before voltage is applied to IN. The device senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for several microseconds before the current-limit circuit can react. The device operates in constant-current mode after the current-limit circuit has responded. In the third condition, the load is increased gradually beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached. The devices are capable of delivering current up to the current-limit threshold without damage. Once the threshold is reached, the device switches into constant-current mode.

Complete shutdown occurs only if the fault is present long enough to activate thermal limiting. The device will remain off until the junction temperature cools approximately 10°C and will then re-start. The device will continue to cycle on/off until the overcurrent condition is removed.

### OCx RESPONSE

Each OCx open-drain output is asserted (active low) during an overcurrent or overtemperature condition on that channel. The output remains asserted until the fault condition is removed. The TPS206xA eliminates false OCx reporting by using internal delay circuitry after entering or leaving an overcurrent condition. This "deglitch" time is approximately 8-ms. This ensures that OCx is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. Overtemperature conditions are not deglitched and assert and de-assert the OCx signal immediately.

#### UNDERVOLTAGE LOCKOUT (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turn-on threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage drop from large current surges.

#### Enable (ENx or ENx)

The logic enable controls the power switch, bias for the charge pump, driver, and other circuits to reduce the supply current. The supply current is reduced to less than 5  $\mu$ A when a logic high is present on ENx, or when a logic low is present on ENx. A logic low input on ENx or a logic high input on ENx enables the driver, control circuits, and power switch for that channel.

#### THERMAL SENSE

The TPS206xA monitors the operating temperature of both power distribution switches with individual thermal sensors. The junction temperature of each channel rises during an overcurrent or short-circuit condition. When the die temperature of a particular channel rises above a minimum of  $135^{\circ}$ C in an overcurrent condition, the internal thermal sense circuitry disables the individual channel in overtemperature to prevent damage. Hysteresis is built into the thermal sensor and re-enables the power switch individually after it has cooled approximately  $10^{\circ}$ C. The power switch cycles on and off until the fault is removed. This topology allows one channel to continue normal operation even if the other channel is in an overtemperature condition. The open-drain overcurrent flag ( $\overline{OCx}$ ) is asserted (active low) corresponding to the channel that is in an overtemperature or overcurrent condition.

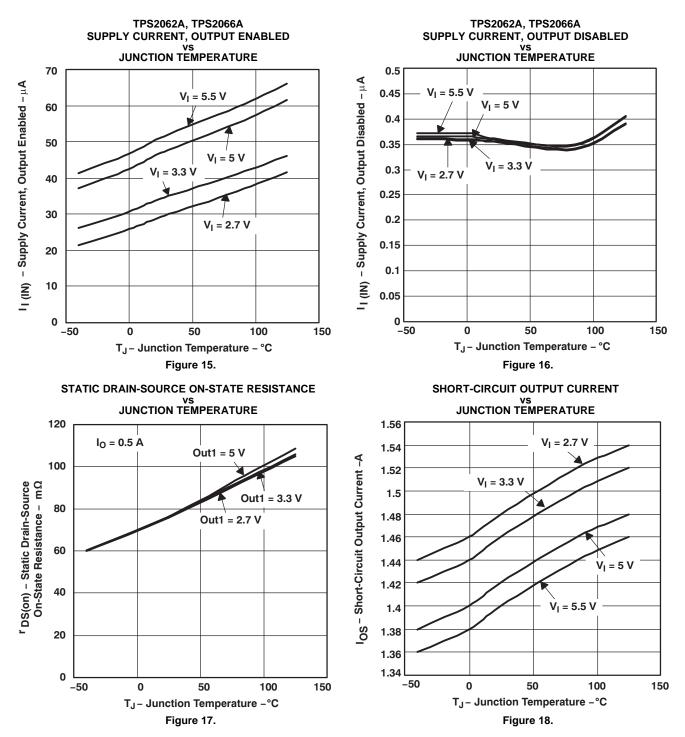

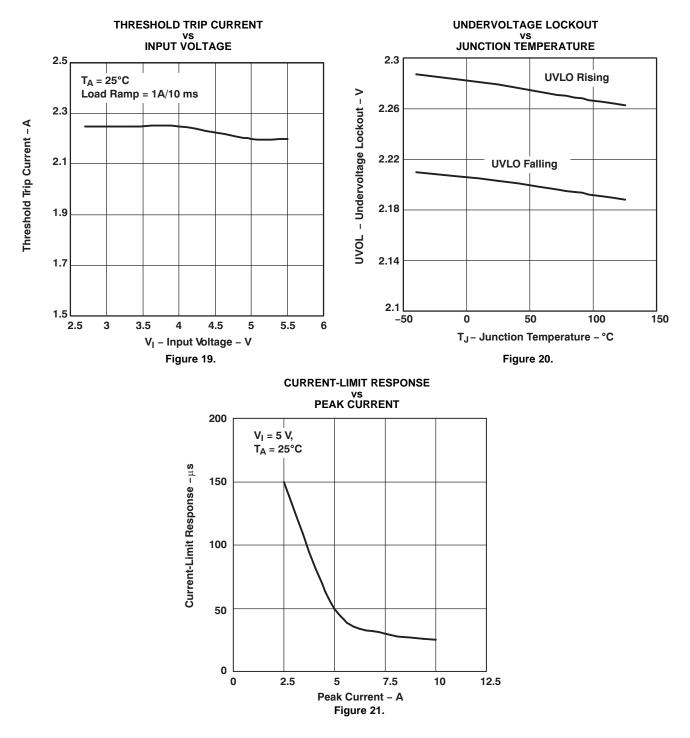

#### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS (continued)**

#### **TYPICAL CHARACTERISTICS (continued)**

### APPLICATION INFORMATION

#### INPUT AND OUTPUT CAPACITANCE

Input and output capacitance improve the performance of the device; the actual capacitance should be optimized for the particular application. For all applications, a 0.01  $\mu$ F to 0.1  $\mu$ F ceramic bypass capacitor between IN and GND is recommended and should be placed as close to the device as possible for local noise de-coupling. This precaution reduces ringing on the input due to power-supply transients . Additional input capacitance may be needed on the input to reduce voltage overshoot from exceeding the absolute maximum voltage of the device during heavy transients.

Placing a high-value electrolytic capacitor on the output pin is recommended when the output load is heavy. Additionally, bypassing the output with a 0.01  $\mu$ F to 0.1  $\mu$ F ceramic capacitor improves the immunity of the device to short-circuit transients.

#### POWER DISSIPATION AND JUNCTION TEMPERATURE

The low on-resistance of the N-channel MOSFETs allows the small surface-mount packages to pass large currents. It is good design practice to check power dissipation to ensure that the junction temperature of the device is within the recommended operating conditions. The below analysis gives an approximation for calculating junction temperature based on the power dissipation in the package. However, it is important to note that thermal analysis is strongly dependent on additional system level factors. Such factors include air flow, board layout, copper thickness and surface area, and proximity to other devices dissipating power. Good thermal design practice must include all system level factors in addition to individual component analysis.

The following procedure shows how to approximate the junction temperature rise due to power dissipation in a single channel. The TPS2062A/66A devices contain two channels, so the total device power must sum the power in each power switch.

Begin by determining the  $r_{DS(on)}$  of the N-channel MOSFET relative to the input voltage and operating temperature. Use the highest operating ambient temperature of interest and read  $r_{DS(on)}$  from the typical characteristics graph as an initial estimate. Power dissipation is calculated by:

$P_{D} = r_{DS(on)} \times I_{OUT}^{2}$  $P_{T} = 2 \times P_{D}$

Where:

P<sub>D</sub> = Power dissipation/channel (W)

$P_T$  = Total power dissipation for both channels (W)

$r_{DS(on)}$  = Power switch on-resistance ( $\Omega$ )

$I_{OUT}$  = Maximum current-limit threshold (A)

Finally, calculate the junction temperature:

$T_J = P_T \times R_{\Theta JA} + T_A$

Where:

$T_A$ = Ambient temperature °C  $R_{OJA}$  = Thermal resistance (°C/W)  $P_T$  = Total power dissipation (W)

Compare the calculated junction temperature with the initial estimate. If they are not within a few degrees, repeat the calculation using the "refined"  $r_{DS(on)}$  from the previous calculation as the new estimate. Two or three iterations are generally sufficient to achieve the desired result. The final junction temperature is highly dependent on thermal resistance  $R_{\theta JA}$ , and thermal resistance is highly dependent on the individual package and board layout. The "Dissipation Rating Table" at the begginng of this document provides example thermal resistances for specific packages and board layouts.

#### **UNIVERSAL SERIAL BUS (USB) APPLICATIONS**

One application for this device is for current-limiting in universal serial bus (USB) applications. The original USB interface was a 12-Mb/s or 1.5-Mb/s, multiplexed serial bus designed for low-to-medium bandwidth PC peripherals (e.g., keyboards, printers, scanners, and mice). As the demand for more bandwidth increased, the USB 2.0 standard was introduced increasing the maximum data rate to 480-Mb/s. The four-wire USB interface is conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub across long cables. Each function must provide its own regulated 3.3 V from the 5-V input or its own internal power supply. The USB specification classifies two different classes of devices depending on its maximum current draw. A device classified as low-power can draw up to 100 mA as defined by the standard. A device classified as high-power can draw up to 500 mA. It is important that the minimum current limit threshold of the current-limiting power switch exceed the maximum current limit draw of the intended application. The latest USB standard should always be referenced when considering the current-limit threshold.

The USB specification defines two types of devices as hubs and functions. A USB hub is a device that contains multiple ports for different USB devices to connect and can be self-powered (SPH) or bus-powered (BPH). A function is a USB device that is able to transmit or receive data or control information over the bus. A USB function can be embedded in a USB hub. A USB function can be one of three types included in the list below.

- Low-power, bus-powered function

- High-power, bus-powered function

- Self-powered function

SPHs and BPHs distribute data and power to downstream functions. The TPS206x6A has higher current capability than required for a single USB port allowing it to power multiple downstream ports.

#### SELF-POWERED AND BUS-POWERED HUBS

A SPH has a local power supply that powers embedded functions and downstream ports. This power supply must provide between 4.75 V to 5.25 V to downstream facing devices under full-load and no-load conditions. SPHs are required to have current-limit protection and must report overcurrent conditions to the USB controller. Typical SPHs are desktop PCs, monitors, printers, and stand-alone hubs.

A BPH obtains all power from an upstream port and often contains an embedded function. It must power up with less than 100 mA. The BPH usually has one embedded function, and power is always available to the controller of the hub. If the embedded function and hub require more than 100 mA on power up, the power to the embedded function may need to be kept off until enumeration is completed. This is accomplished by removing power or by shutting off the clock to the embedded function. Power switching the embedded function is not necessary if the aggregate power draw for the function and controller is less than 100 mA. The total current drawn by the bus-powered device is the sum of the current to the controller, the embedded function, and the downstream ports, and it is limited to 500 mA from an upstream port.

#### LOW-POWER BUS-POWERED AND HIGH-POWER BUS-POWERED FUNCTIONS

Both low-power and high-power bus-powered functions obtain all power from upstream ports. Low-power functions always draw less than 100 mA; high-power functions must draw less than 100 mA at power up and can draw up to 500 mA after enumeration. If the load of the function is more than the parallel combination of 44  $\Omega$ and 10 µF at power up, the device must implement inrush current limiting.

SLVS798F-JANUARY 2008-REVISED NOVEMBER 2008

### USB POWER-DISTRIBUTION REQUIREMENTS

USB can be implemented in several ways regardless of the type of USB device being developed. Several power-distribution features must be implemented.

- SPHs must:

- Current-limit downstream ports

- Report overcurrent conditions

- BPHs must:

- Enable/disable power to downstream ports

- Power up at <100 mA

- Limit inrush current (<44  $\Omega$  and 10  $\mu$ F)

- Functions must:

- Limit inrush currents

- Power up at <100 mA</li>

The feature set of the TPS2062A/66A meets each of these requirements. The integrated current-limiting and overcurrent reporting is required by self-powered hubs. The logic-level enable and controlled rise times meet the need of both input and output ports on bus-powered hubs and the input ports for bus-powered functions.

8-Dec-2018

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|-------------------------|---------|

| TPS2062AD        | ACTIVE        | SOIC         | D                  | 8    | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2062A                   | Samples |

| TPS2062ADR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2062A                   | Samples |

| TPS2062ADRBR     | ACTIVE        | SON          | DRB                | 8    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2062                    | Samples |

| TPS2062ADRBT     | ACTIVE        | SON          | DRB                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2062                    | Samples |

| TPS2062ADRBTG4   | ACTIVE        | SON          | DRB                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2062                    | Samples |

| TPS2066AD        | ACTIVE        | SOIC         | D                  | 8    | 75             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2066A                   | Samples |

| TPS2066ADR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2066A                   | Samples |

| TPS2066ADRBR     | ACTIVE        | SON          | DRB                | 8    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2066                    | Samples |

| TPS2066ADRBT     | ACTIVE        | SON          | DRB                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2066                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

8-Dec-2018

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

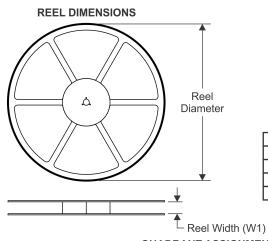

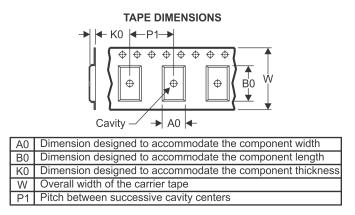

#### TAPE AND REEL INFORMATION

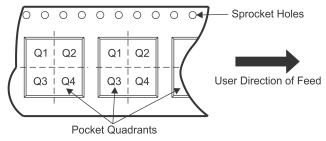

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS2062ADR                  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2062ADRBR                | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

| TPS2062ADRBT                | SON             | DRB                | 8 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

| TPS2066ADR                  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2066ADRBR                | SON             | DRB                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

| TPS2066ADRBT                | SON             | DRB                | 8 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.0        | 8.0        | 12.0      | Q2               |

Texas Instruments

www.ti.com

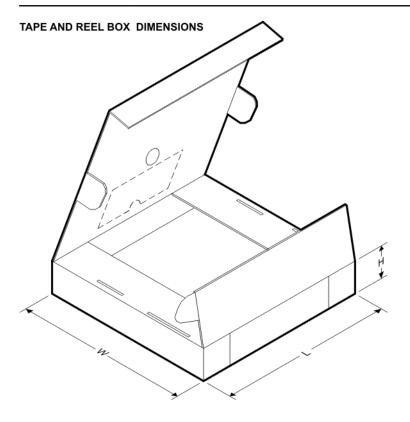

# PACKAGE MATERIALS INFORMATION

3-Aug-2017

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2062ADR   | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2062ADRBR | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 35.0        |

| TPS2062ADRBT | SON          | DRB             | 8    | 250  | 203.0       | 203.0      | 35.0        |

| TPS2066ADR   | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2066ADRBR | SON          | DRB             | 8    | 3000 | 346.0       | 346.0      | 35.0        |

| TPS2066ADRBT | SON          | DRB             | 8    | 250  | 203.0       | 203.0      | 35.0        |

### **GENERIC PACKAGE VIEW**

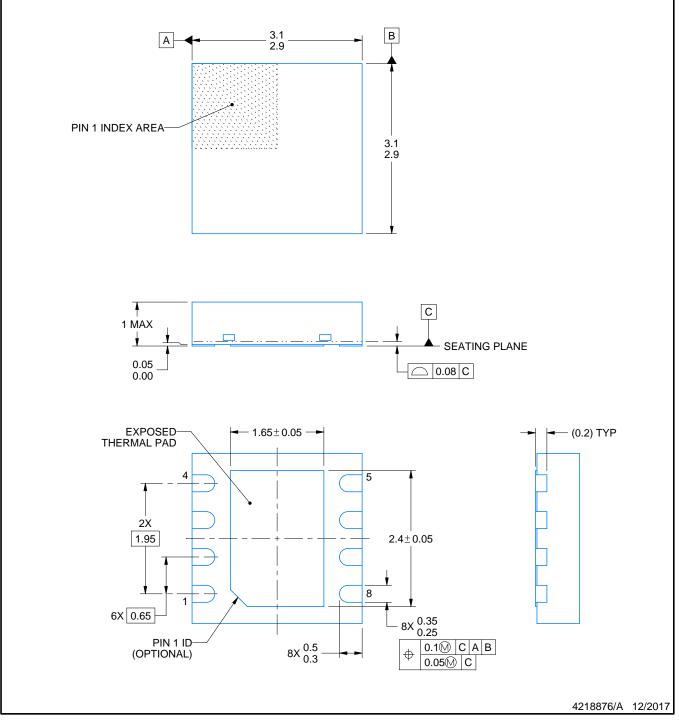

# VSON - 1 mm max height PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4203482/L

# DRB0008B

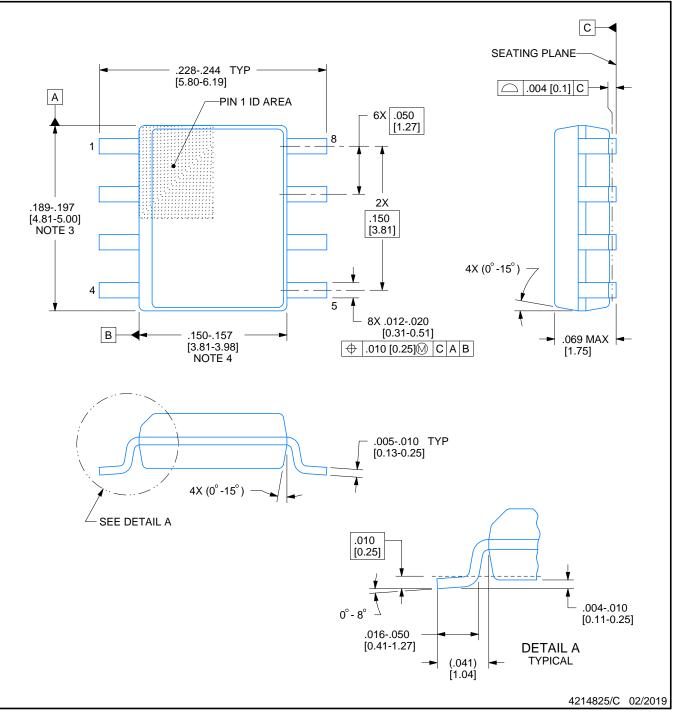

# **PACKAGE OUTLINE**

### VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

# **DRB0008B**

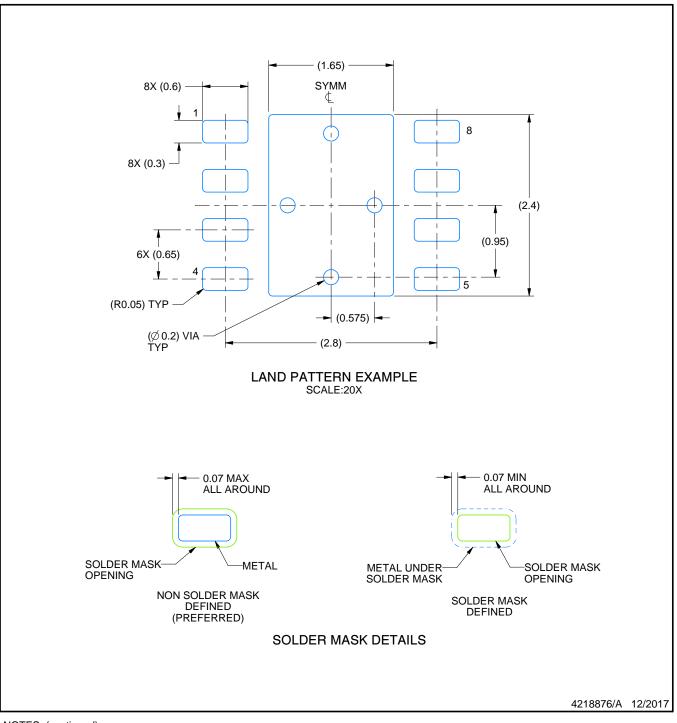

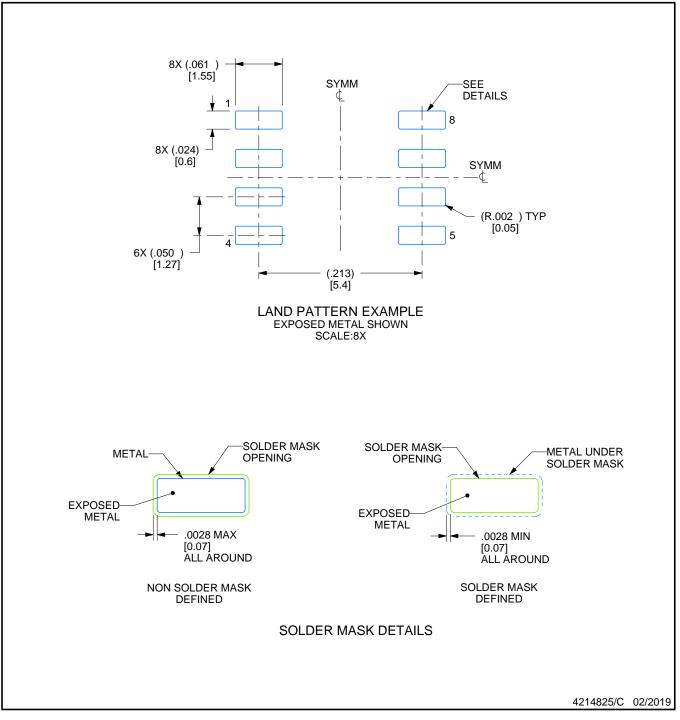

# **EXAMPLE BOARD LAYOUT**

### VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# **DRB0008B**

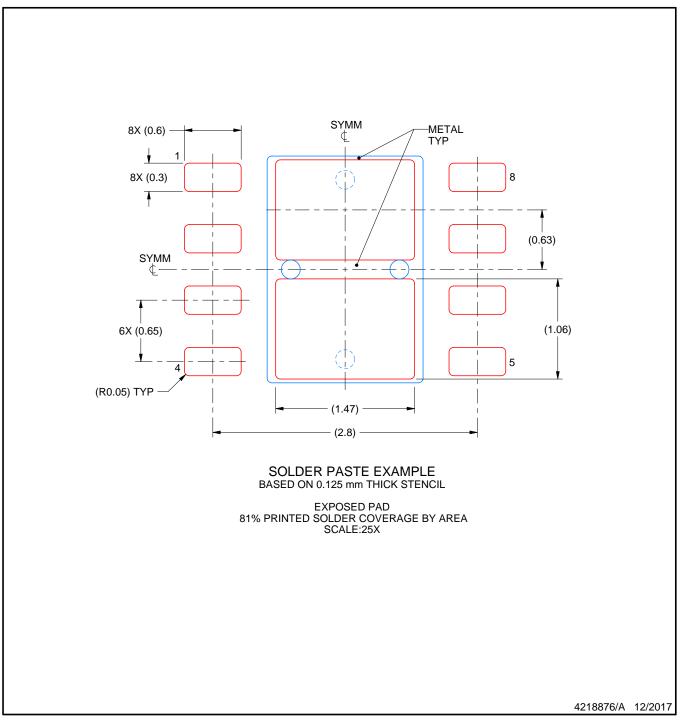

# **EXAMPLE STENCIL DESIGN**

### VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# D0008A

# **PACKAGE OUTLINE**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

# D0008A

# **EXAMPLE BOARD LAYOUT**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# D0008A

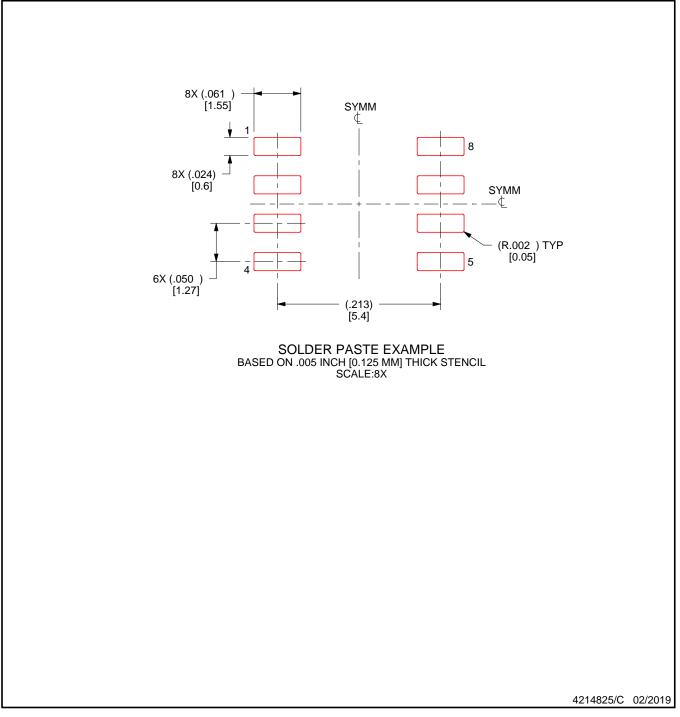

# **EXAMPLE STENCIL DESIGN**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated